## Fundamentals of Electronics Exam

Prof. dr. E. Chicca, dr. J.S. Blijleven

#### Information

Welcome to the Fundamental of Electronics exam. Please read carefully the information below.

#### How to write your solution

Please use a **pen** and not a pencil. Make sure your **hand writing** is understandable by others. **Drawings** do not need to be beautiful/perfect but it is important that they are easy to understand and there are no ambiguities (e.g. a gate which could be an OR or an AND, but it is not clear which one it is, label it to avoid confusion).

Each solution has to be justified and the steps to get there have to be explicitly written down, only providing the final outcome will lead to zero points. On every page please indicate which problem you are working on. If you separate the pages please indicate your name and student ID on every page.

For your convenience, you can find a page with basic equations related to the course material at the end of this document.

| Full name: | Student ID: |

|------------|-------------|

This work is licensed under Creative Commons Attribution-ShareAlike 4.0 Unported (CC BY-SA 4.0) https://creativecommons.org/licenses/by-sa/4.0/ by Elisabetta Chicca, Jelle Blijleven, Lloyd Peschl, Madison Cotteret, Djano Persoon, Kenan Thalens (c) University of Groningen 2024.

## Problem 1 (22 points)

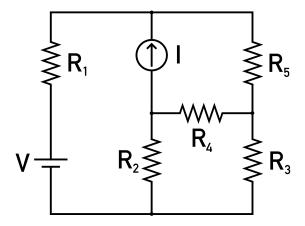

Consider the circuit given below with values  $R_1 = 1k\Omega$ ,  $R_2 = 3k\Omega$ ,  $R_3 = 3k\Omega$ ,  $R_4 = 3k\Omega$ , V = 12V and I = 3mA.

(a) (5 points) Calculate the equivalent resistance  $R_{\rm eq}$  as seen from  $R_5$  (load resistor).

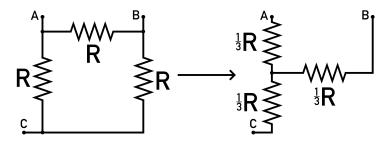

Using the basic rules of parallel and series circuits, a loop of three identical resistors cannot be further simplified. The group can however be transformed into an equivalent resistor network. Shown below is the Wye-Delta transformation for a network of three resistors with the same value R.

The network on the left is equivalent to that on the right, allowing for further simplification of certain resistor networks.

- (b) (12 points) In the given circuit, the resistor network consisting of  $R_2$ ,  $R_3$  and  $R_4$  can be transformed into an equivalent network using the Wye-Delta transformation. Using the variables given above, determine the Norton short circuit current,  $I_{SC}$ , as seen from  $R_5$ .

- (c) (2 points) Select the true statements.

- (a) A Norton circuit consists of a current source and a resistor in series.

- (b) A Thévenin circuit consists of a voltage source and a resistor in parallel.

- (c) A Norton circuit consists of a current source and a resistor in parallel.

- (d) A Thévenin circuit consists of a voltage source and a resistor in series.

- (d) (3 point) Draw the Norton and Thévenin equivalent circuits considering  $R_5$  as a load resistor. Provide the expression for the open circuit voltage  $V_{\rm OC}$  in terms of the variable  $I_{\rm SC}$ .

## Problem 1 - solution (22 points)

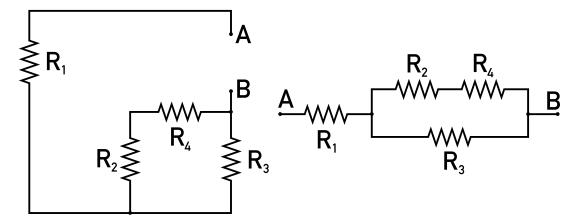

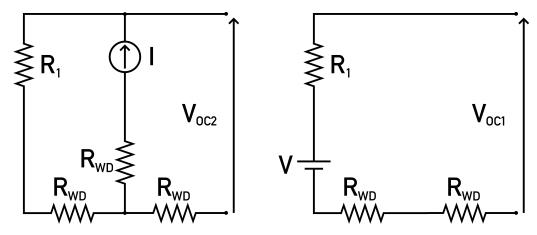

(a) (4 points) To calculate the equivalent resistance  $R_{\rm eq}$  as seen from  $R_5$ , all voltage sources are shorted and all current sources are open.  $R_5$  is also replaced by two open nodes A and B.

Figure 1: Circuit with voltage sources shorted and current sources open shown on the left. Simplified resistor network on the right.

The resistance  $R_{\rm AB}$  therefore corresponds to:

$$R_{AB} = R_1 + (R_2 + R_4)//R_3 = R_1 + \frac{(R_2 + R_4)R_3}{(R_2 + R_4) + R_3}$$

Hence  $R_{AB} = \underline{R_{eq} = 3k\Omega}$ .

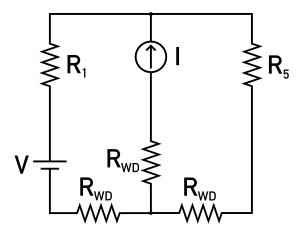

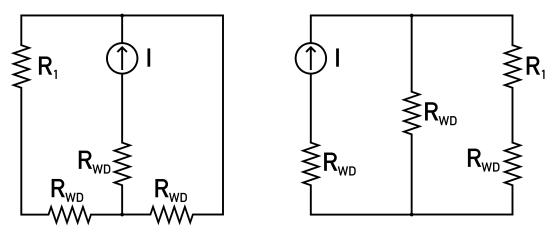

(b) (12 points) Using the Wye-Delta transformation on the circuit given, specifically for the network with resistors  $R_2$ ,  $R_4$  and  $R_3$ , yields an equivalent circuit as shown in Figure 2.

Figure 2: Wye-Delta transformation applied on the original circuit.

With the given values in the problem, it can be seen that  $R_{\rm WD} = \frac{1}{3}R_2 = \frac{1}{3}R_3 = \frac{1}{3}R_4$  such that  $R_{\rm WD} = 1000\Omega$ . Using this circuit, the short circuit current  $I_{\rm SCI}$  as seen from  $R_5$  can be found. **Solution I**: First, the voltage source is shorted. This gives Figure 3.

Figure 3: Circuit simplification to find  $I_{SCI}$ .

The total resistance is therefore

$$R_{\text{TOT}} = R_{\text{WD}} + \frac{R_{\text{WD}}(R_1 + R_{\text{WD}})}{R_{\text{WD}} + (R_1 + R_{\text{WD}})} = 1000 + \frac{1000(R_1 + 1000)}{1000 + (R_1 + 1000)}$$

which corresponds to a numerical value of  $R_{\text{TOT}} = 1666.67\Omega$ . Using this total resistance, the voltage across I can be calculated as  $V_I = IR_{\text{TOT}} = 5\text{V}$ . Looking at the left image of Figure 3, the current flowing through the right-most branch must be equal to:

$$I_{SCI} = 5/R_{WD} = 2mA$$

Alternatively, the current divider can be used on the right diagram in Figure 3 to find the current flowing through the central wire (in the middle). Using the current divider formula

$$I_{\rm SCI} = \frac{R_1 + R_{\rm WD}}{(R_1 + R_{\rm WD}) + R_{\rm WD}} I = \frac{1000 + 1000}{(1000 + 1000) + 1000} \cdot 3\text{mA}$$

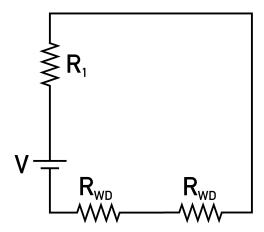

which is equal to  $I_{SCI} = 2\text{mA}$ . Next the current source is open. This gives Figure 4.

Figure 4: Circuit simplification to find  $I_{SCV}$ .

The total resistance simply corresponds to

$$R_{\text{TOT}} = R_1 + R_{\text{WD}} + R_{\text{WD}}$$

which is equal to  $R_{\text{TOT}} = 3000\Omega$ . The current across the voltage source is therefore

$$\underline{I_{\rm SCV} = 12/R_{\rm TOT} = 4\text{mA}}$$

By then using the superposition principle,

$$I_{SC} = I_{SCI} + I_{SCV} = 6 \text{mA}$$

**Solution II**: It can also be solved alternatively. In this approach, the open circuit voltages of both cases, shorted voltage source and open current source are considered, as shown in Figure 5.

Figure 5: Circuits with shorted terminals.

For the left-most circuit, the voltage  $V_{\rm OC2}$  is equal to the voltage across the left-most branch such that

$$V_{\text{OC2}} = I(R_1 + R_{\text{WD}}) = 3\text{mA} \cdot 2\text{k}\Omega$$

and  $V_{\rm OC2}=6{\rm V}$ . For the right-most circuit, the voltage  $V_{\rm OC1}$  is equal to V since there is no current loop so  $V_{\rm OC1}=12{\rm V}$ . Since  $V_{\rm OC}=V_{\rm OC1}+V_{\rm OC2},\ V_{\rm OC}=18{\rm V}$ . Using the equivalent resistance calculated in part (a):

$$I_{\rm SC} = \frac{18 \text{V}}{3 \text{k} \Omega} = 6 \text{mA}$$

- (c) (2 points) Statements (d) and (c) are correct.

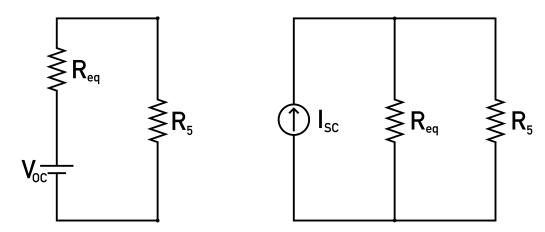

- (d) (3 points) The Norton and Thévenin equivalent circuits correspond to Figure 6. The Thévenin equivalent voltage can be re-written in terms of the Norton equivalent current as  $V_{\rm OC} = I_{\rm SC} R_{eq}$ .

Figure 6: Thévenin (left) and Norton (right) equivalent circuits.  $V_{\rm OC} = I_{\rm SC} R_{\rm eq}$ .

## Problem 2 (16 points)

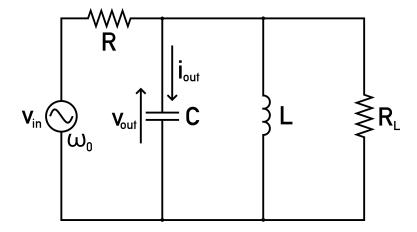

Consider the RLC circuit shown below. Assume sinusoidal regime, ideal components and the following parameters: C = 0.25 F, L = 1 H,  $R = 30 \Omega$ ,  $R_L = 10 \Omega$ ,  $\omega_0 = 2 \text{rads}^{-1}$ .

(a) (3 points) Describe, without any calculations and only reasoning, the behaviour of

$$H(\omega) = \frac{i_{\text{out}}}{v_{\text{in}}}$$

for low  $(\omega \to 0)$  and high  $(\omega \to \infty)$  frequencies.

- (b) (8 points) Using the parameter values given above, provide an expression in its simplest form for the transfer function  $H(\omega_0)$ . Hint: Check early on if replacing variables with their values leads to simple expressions.

- (c) (3 points) Suppose  $R_L$  is a removable load. Determine the equivalent impedance of the circuit as seen from  $R_L$  as a function of the components in terms of the variables (e.g. not using the given values C=0.25F, etc.) and find an expression of this kind:

$$Z_{\rm eq} = \frac{1}{Re + jIm}$$

where Re indicates a purely real part and Im a purely imaginary part.

(d) (2 points) Suppose the transfer function of a different RLC circuit but with the same parameters is considered:

$$H(\omega) = \frac{RR_L}{R + R_L + j[\omega L - \frac{1}{\omega C}]}$$

Determine the angular frequency  $\omega_{\text{max}}$  at which the transfer function is at a maximum and  $H(\omega_{\text{max}})$ .

7

#### Problem 2 - solution (16 points)

(a) (3 points) For low frequencies ( $\omega \to 0 \text{ rads}^{-1}$ ) the capacitor impedance  $Z_C \to \infty$ . Thus the capacitor may be replaced by an open circuit so no current flows through the capacitor and  $i_{out} = 0$  and so  $H(\omega) = 0$ .

For high frequencies ( $\omega \to \infty \, \mathrm{rads}^{-1}$ ) the capacitor impedance  $Z_C \to 0$ . Therefore the impedance of the parallel branch  $Z_{\parallel} \to 0$ , and all current through the parallel branch goes through the capacitor. The current through R will be  $v_{\rm in}/(R+Z_{\parallel}) \to v_{\rm in}/R$ , therefore  $H(\omega) \to 1/R$ .

(b) (8 points) The net impedance  $Z_{\parallel}$  of the components C, L and  $R_L$  are related by the expression:

$$\frac{1}{Z_{\parallel}} = j\omega C - \frac{j}{\omega L} + \frac{1}{R_L}$$

Substituting in the appropriate values:

$$\frac{1}{Z_{\parallel}} = 0.5j - 0.5j + 0.1 = 0.1$$

$$Z_{\parallel} = 10\Omega$$

The new simplified circuit consists of the voltage source and R and  $Z_{\parallel}$  in series with one another. The total circuit impedance is given by

$$Z_{\rm tot} = Z_{\parallel} + R = 10\Omega + 30\Omega = 40\Omega$$

**Solution I**: Using the potential divider to obtain  $v_{\text{out}}$  across the impedance  $Z_{\parallel}$ :

$$v_{\rm out} = \frac{Z_\parallel}{Z_{\rm tot}} v_{\rm in} = \frac{Z_\parallel}{Z_\parallel + R} v_{\rm in} = \frac{10\Omega}{10\Omega + 30\Omega} v_{\rm in} = \frac{1}{4} v_{\rm in}$$

The current through the capacitor C is thus

$$i_{\text{out}} = v_{\text{out}}/Z_c = \frac{1}{4}(j\omega_0 C)v_{\text{in}} = \frac{1}{8}jv_{\text{in}}$$

and thus the transfer function  $H(\omega_0)$  is given by:

$$\underline{H(\omega_0) = \frac{i_{\text{out}}}{v_{\text{in}}} = \frac{j}{8}\Omega^{-1} = 0.125j\Omega^{-1}}$$

Since the phrasing of the question was not too clear as to whether the function should be evaluated at  $H(\omega_0)$  or not, partial marks are given for the correct expression in terms of the impedance variables and full marks for the final expression,

$$H(\omega_0) = i_{\rm out}/v_{\rm in} = \frac{1}{Z_c} v_{\rm out}/v_{\rm in} = \frac{1}{Z_c} \frac{Z_{\parallel}}{Z_{\parallel} + R} = \frac{j \omega_0^2 C L R_L}{\omega_0 L R_L + R(j R_L [\omega_0^2 C L - 1] + \omega_0 L)}$$

where  $Z_{\parallel}$  is defined above and the full expression in terms of the variables is given.

**Solution II**: The current divider can also be used to solve this problem. The first step is to calculate the parallel impedance of L and  $R_L$ :

$$\frac{1}{Z_{\rm LR_L}} = \frac{-j}{\omega L} + \frac{1}{R_L} \Rightarrow Z_{\rm LR_L} = \frac{10}{1 - 5j} \Omega$$

Next, an expression for  $i_{\text{out}}$  in terms of  $i_{\text{in}}$  can be determined using the current divider formula:

$$i_{\rm out} = \frac{Z_{\rm LR_L}}{Z_{\rm LR_L} + Z_C} i_{\rm in} \Rightarrow i_{\rm out} = 5j \cdot i_{\rm in}$$

Using  $Z_{\text{tot}}$  calculated previously, an expression for  $i_{\text{in}}$  can be found in terms of  $v_{\text{in}}$ , which leads directly to the final answer:

$$i_{\rm in} = \frac{v_{\rm in}}{Z_{\rm tot}} = \frac{v_{\rm in}}{40} \Rightarrow \underline{H(\omega_0) = \frac{i_{\rm out}}{v_{\rm in}} = \frac{j}{8}\Omega^{-1} = 0.125j\Omega^{-1}}$$

(c) (3 points) For the equivalent impedance considering  $R_L$ , the voltage supply is shorted such that R, C and L are in parallel with one another. It then follows that

$$\begin{split} \frac{1}{Z_{\rm eq}} &= \frac{1}{R} + \frac{1}{Z_C} + \frac{1}{Z_L} \\ &= \frac{1}{R} + j \left[ \omega C - \frac{1}{\omega L} \right] \\ Z_{\rm eq} &= \frac{1}{\frac{1}{R} + j \left[ \omega C - \frac{1}{\omega L} \right]} \end{split}$$

(d) (2 points) To find the angular frequency  $\omega_{\text{max}}$  at which the transfer function is at a maximum, the imaginary part of the expression must be equal to zero, hence:

$$\omega_{\text{max}}L - \frac{1}{\omega_{\text{max}}C} = 0$$

$$\omega_{\text{max}}^2 = \frac{1}{LC}$$

$$\omega_{\text{max}} = \frac{1}{\sqrt{LC}}$$

$$\omega_{\text{max}} = 2\text{rads}^{-1}$$

Therefore,  $H(\omega_{\text{max}}) = \underline{7.5\Omega^{-1}}$ .

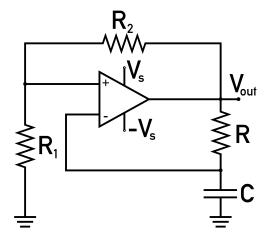

#### Problem 3 (18 points)

Consider the following oscillator circuit with an operational amplifier supplied by a mimimum and maximum voltage of  $-V_s$  and  $V_s$  respectively.

(a) (2 points) State the two golden rules of operational amplifiers.

Suppose the initial state of the circuit corresponds to  $V_{\text{out}} = V_s$  and  $V_- = -V_+$ . The capacitor in the RC network will subsequently charge due to  $V_{\text{out}}$  and influence the voltage  $V_-$ .

(b) (4 points) As the circuit runs,  $V_{-}$  increases until eventually  $V_{-} > V_{+}$ . When this happens, the output voltage changes to  $V_{\text{out}} = -V_{s}$ , resulting in the capacitor discharging. Under these new conditions, describe how  $V_{\text{out}}$  and  $V_{-}$  will change once  $V_{-} < V_{+}$ .

The general equation describing the voltage of a charging RC capacitor corresponds to

$$V(t) = V_0 \left[ 1 - \exp\left(\frac{-t}{RC} + A\right) \right]$$

for  $t \ge 0$  where V(t) is the voltage across the capacitor,  $V_0$  is the voltage across the RC combination, t is the time elapsed and A is a constant that accounts for an initial voltage not equal to zero.

(c) (12 points) By determining an expression for  $V_+$  in terms of  $V_{\text{out}}$ ,  $R_1$  and  $R_2$  and by using the general equation for a charging RC capacitor, determine an expression for the time, T, it takes for the voltage, V(t), to go from the initial state  $V_- = -V_+$  to the state  $V_- = V_+$ . Using this result, determine the frequency of the circuit.

# Problem 3 - solution (18 points)

- (a) (2 points) 1. No current flows into the inputs and 2. The operational amplifier will change the output such that the two inputs are equal to one another.

- (b) (4 points) When  $V_{-} < V_{+}$ , then according to the golden rules, the output will change such that the two inputs are equal. The only way it can do this is by changing the sign of the output voltage, thereby forcing the capacitor to charge once again, hence completing one cycle. Therefore  $V_{\text{out}} = V_s$  and  $V_{-}$  will begin rising again.

- (c) (12 points) To solve this problem, we first need to calculate the values of  $V_+$ . We can apply the potential divider to obtain

$$V_{+} = \frac{R_1}{R_1 + R_2} V_{\text{out}} = \pm \frac{R_1}{R_1 + R_2} V_s$$

where we've added that  $V_{\text{out}}$  takes the values  $\pm V_s$  only. To apply the RC charging equation, we must determine the constant A. To do this, two key parts need to be recognized. First, in this particular case,  $V_0 = V_{\text{out}}$  with  $V_{\text{out}}(t=0) = V_s$ . Second,  $V(t) = V_- = -V_+$  with  $V(t=0) = -V_+$  and  $V(t=T) = V_+$ . By applying these conditions, A and T can be solved for. Using  $V(t=0) = -V_+$  and  $V_{\text{out}} = V_s$  at t=0:

$$-V_s \frac{R_1}{R_1 + R_2} = V_s \left[ 1 - \exp(A) \right]$$

$$\exp(A) = \frac{2R_1 + R_2}{R_1 + R_2}$$

$$A = \ln \frac{2R_1 + R_2}{R_1 + R_2}$$

We then solve  $V(t = T) = V_+$ :

$$V(t = T) = \frac{R_1}{R_1 + R_2} V_s = V_s \left[ 1 - \exp\left(\frac{-T}{RC} + A\right) \right]$$

$$\exp\left(\frac{-T}{RC} + A\right) = \frac{R_2}{R_1 + R_2}$$

$$T = -RC \ln \frac{R_2}{R_1 + R_2} + RCA$$

$$T = RC \ln \frac{R_1 + R_2}{R_2} + RC \ln \frac{2R_1 + R_2}{R_1 + R_2}$$

$$T = RC \ln \frac{2R_1 + R_2}{R_2}$$

Since this time represents only half a cycle, the total time  $T_{\text{tot}} = 2T$ . From this, the reciprocal corresponds to the frequency.

$$f = \frac{1}{T_{\text{tot}}} = \frac{1}{2RC \ln \frac{2R_1 + R_2}{R_2}}$$

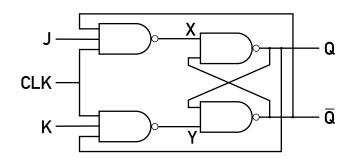

# Problem 4 (14 points)

Shown below is the logic circuit of a positively edge-triggered JK flip-flop with outputs Q and  $\overline{Q}$  and its truth table (to be filled).

| CLK | J | K | X | Y | Q |

|-----|---|---|---|---|---|

|     | 0 | 0 |   |   |   |

|     | 0 | 1 |   |   |   |

|     | 1 | 0 |   |   |   |

|     | 1 | 1 |   |   |   |

| x   | 0 | 0 |   |   |   |

| x   | 0 | 1 |   |   |   |

| X   | 1 | 0 |   |   |   |

| x   | 1 | 1 |   |   |   |

|     |   |   | ш |   | I |

- (a) (5 points) The clock (denoted CLK) produces a binary signal, which, in conjunction with the inputs J and K, can update the circuit output. By analyzing the circuit, fill in the given truth table. Provide the correct bit (0,1) for the two internal variables X and Y. Fill the column reserved for Q with the appropriate content: 0, 1, Toggle (change current output state) and Latch (keep current output state).

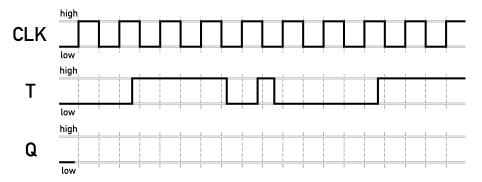

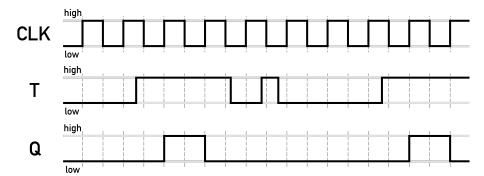

- (b) (4 points) Consider the case where the inputs J and K are fused together into one new input, T. Draw the resultant signal waveform of the output Q in the diagram below. Assume ideal gates (no signal delay).

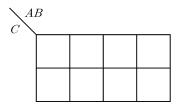

(c) (3 points) Consider the following unsimplified boolean expression:

$$Z = \bar{A}\bar{B}C + A\bar{B}\bar{C} + A\bar{B}C + AB\bar{C} + ABC$$

By filling in and using the Karnaugh map given below, determine the simplified expression. Clearly show on the Karnaugh map how you derived the simplified expressions.

(d) (2 points) Consider a new boolean expression X:

$$\overline{X} = A + \bar{B}\bar{C}$$

12

Negate the expression for  $\overline{X}$  and simplify using boolean algebra.

# Problem 4 - solution (14 points)

(a) (5 points) The filled truth table of the JK flip-flop corresponds to the following:

| CLK | J | K | X      | Y      | Q      |

|-----|---|---|--------|--------|--------|

|     | 0 | 0 | 1      | 1      | latch  |

|     | 0 | 1 | 1      | 1      | 0      |

|     | 1 | 0 | 1      | 1      | 1      |

|     | 1 | 1 | 1 or 0 | 0 or 1 | toggle |

| x   | 0 | 0 | 1      | 1      | latch  |

| x   | 0 | 1 | 1      | 1      | latch  |

| x   | 1 | 0 | 1      | 1      | latch  |

| x   | 1 | 1 | 1      | 1      | latch  |

(b) (4 points) The JK flip-flop is positively edge-triggered, meaning the rising edge of the clock produces a signal input. The waveform of Q should resemble the following:

(c) (3 points) The boolean expression provided can be converted into the following Karnaugh map:

| CAR | 00 | 01 | 11 | 10 |

|-----|----|----|----|----|

| 0   | 0  | 0  | 1  | 1  |

| 1   | 1  | 0  | 1  | 1  |

By identifying the highlighted minterm groups, the simplified expression for Z can immediately be obtained as:

$$Z = A + \bar{B}C$$

(d) (2 points) The given expression for  $\overline{X}$  should be negated again to  $\overline{\overline{X}}$ . By doing so and using De Morgan's laws to simplify, the following is obtained

$$\overline{\overline{X}} = \overline{A + \overline{B}\overline{C}}$$

$$= \overline{A} \cdot \overline{\overline{B}\overline{C}}$$

$$X = \overline{A}(B + C)$$